Simulation netlist will contain all netlist optimizations that occurred during placement and routing. Full placement and routing has taken place however retiming of registers into Hyper register locations has not taken place yet. Simulation netlist will contain all netlist optimizations that occurred during placement.

Placement has occurred but no routing or retiming into Hyper registers has taken place at this stage. No placement has taken place at this stage. 3) Perform a full compilation of the design.įull compilation will provide the ability to generate a simulation netlist for all stages (snapshots) of the compilation (synthesized, planned, placed, routed, retimed, final) If they don’t then they will remain as “X” which will then propagate through the design during simulation. If the registers have a sufficient reset, then they will be cleared through the assertion of the design reset. The “EDA_FORCE_GATE_LEVEL_REG_INIT_X” assignment will initialize all registers in the design to “X”. Set_global_assignment -name EDA_FORCE_GATE_LEVEL_REG_INIT_X ON -section_id eda_simulation Set_global_assignment -name EDA_OUTPUT_DATA_FORMAT "VERILOG HDL" -section_id eda_simulation

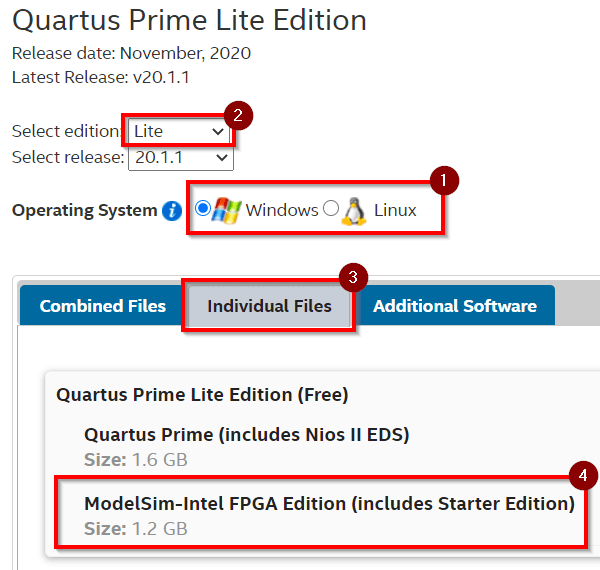

Set_global_assignment -name EDA_TIME_SCALE "1 ps" -section_id eda_simulation qsf file: set_global_assignment -name EDA_SIMULATION_TOOL VCS Which will write the following assignments into the. Go to the Assignments > Settings > EDA Tool Settings>Simulation page and apply the appropriate simulator settings. qsf file: set_instance_assignment -name PARTITION sub_block -to U1 -entity Project_Top 2) Apply appropriate simulator settings in the EDA Tool Settings page. This will then generate the appropriate constraint in the.

The easiest way to create the assignment is to perform the following steps in the Intel® Quartus® Prime Software GUI:Ī) Synthesize the top-level project in the Intel® Quartus® Prime Software GUI.ī) Use the Project Navigator to locate the level of hierarchy that instantiates the IP sub-block for which the gate-level simulation netlist is required.Ĭ) Right-click on the sub-block instance and select “Design Partition > Type = Default” as shown below:Ī. The syntax for the design partition assignment is shown below set_instance_assignment -name PARTITION -to -entity To enable the generation of a gate-level simulation netlist for a sub-block within the context of a top-level project (EG a specific lower-level IP) then a design partition assignment needs to be created for the sub-block instantiation. How do I generate gate-level simulation netlists for sub-modules in my design and test for sensitivity to register power-up values? 1) Apply a design partition assignment on the appropriate level of hierarchy.

0 kommentar(er)

0 kommentar(er)